### TD9721

## **General Description**

The TD9721 is a stereo, differential input, single supply, and cap-free line driver, which is available in SOP-14 and TSSOP-14 packages.

The TD9721 is ground-reference output, and doesn't need the output capacitors for DC blocking. The advantages of eliminating the output capacitor are saving the cost, eliminating component height, and improving the low frequency response.

The external gain setting is recommended using from  $\pm 1 \text{V/V}$  to  $\pm 10 \text{V/V}$ . High PSRR provides increased immunity to noise and RF rectification. TD9721 has shutdown and under-voltage detector function for Depop solution. The TD9721 is capable of driving 2.1Vrms at 3.3V into 2.5k $\Omega$  load, and provides short-circuit and thermal rotection.

### **Features**

- Operating Voltage: 3V~3.6V

- Differential Input

- Ground Reference Output

- No Output Capacitor Required (for DC Blocking)

- Save the PCB Space

- Reduce the BOM Costs

- Improve the Low Frequency Response

- Low Noise and THD+N

- SNR > 108dB

- Noise < 8uV<sub>rms</sub>

- THD+N < 0.02% at 20Hz~20kHz

- Output Voltage Swing Can Reach 2.1Vrms/Chinto2.5 k $\Omega$  at  $V_{\text{DD}}$ =3.3V

- High PSRR: 80dB at 217Hz

- Fast Start-up Time: 500us

- Integrate the De-Pop Circuitry

- Thermal and Short-Circuit Protection

- Surface-Mount Packaging

- SOP-14

- TSSOP-14

- Lead Free and Green Devices Available(RoHS Compliant)

### **Applications**

- Set-Top Boxes

- CD/DVD Players

- LCD TVs

- HTIBs (Home Theater in Box)

TD9721

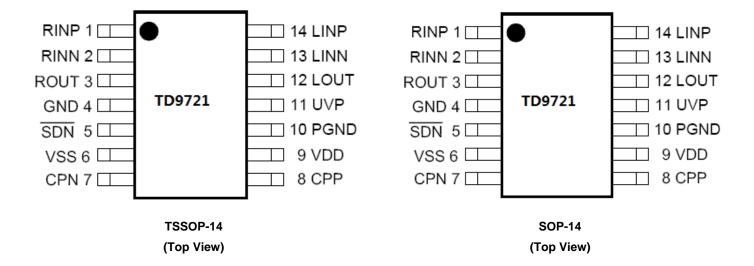

# **Pin Configurations**

## **Pin Description**

| NO. | NAME | I/O/P | FUNCTION                                                                                      |

|-----|------|-------|-----------------------------------------------------------------------------------------------|

| 1   | RINP | I     | Right channel non-inverting input.                                                            |

| 2   | RINN | I     | Right channel inverting input.                                                                |

| 3   | ROUT | 0     | Right channel output.                                                                         |

| 4   | GND  | Р     | Signal ground.                                                                                |

| 5   | SDN  | _     | Shutdown mod control input signal, pull low for shutdown headphone driver. This pin should be |

| 5   | SDN  | -     | connect a $100\Omega$ Protection Resistor.                                                    |

| 6   | VSS  | Р     | Headphone driver negative power supply.                                                       |

| 7   | CPN  | 1/0   | Charge pump flying capacitor negative connection.                                             |

| 8   | CPP  | 1/0   | Charge pump flying capacitor positive connection.                                             |

| 9   | VDD  | Р     | Supply voltage input.                                                                         |

| 10  | PGND | Р     | Power ground.                                                                                 |

| 11  | UVP  | I     | Under voltage protection input. Floating or Pull "H" to disable this function.                |

| 12  | LOUT | 0     | Left channel output.                                                                          |

| 13  | LINN | I     | Left channel inverting input.                                                                 |

| 14  | LINP | I     | Left channel non-inverting input.                                                             |

TD9721

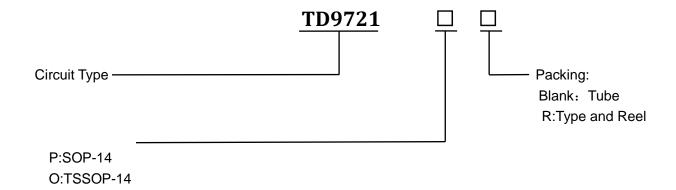

# **Ordering Information**

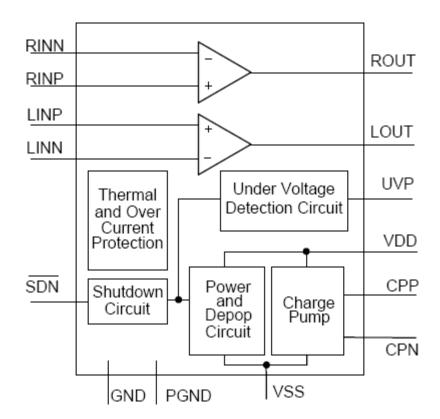

### **Functional Block Diagram**

TD9721

# **Absolute Maximum Ratings**

| Symbol                                                           | Parameter                            | Rating                                         | Unit |

|------------------------------------------------------------------|--------------------------------------|------------------------------------------------|------|

| V <sub>PGND_GND</sub>                                            | PGND to GND Voltage                  | -0.3 to 0.3                                    |      |

| V <sub>DD</sub>                                                  | Supply Voltage (VDD to GND and PGND) | -0.3 to 4                                      |      |

| V <sub>SDN</sub>                                                 | Input Voltage (SDN to GND)           | $V_{GND}$ -0.3 to $V_{DD}$ +0.3                |      |

| V <sub>ss</sub>                                                  | VSS to GND and PGND Voltage          | -6 to 0.3                                      | V    |

| V <sub>out</sub>                                                 | ROUT and LOUT to GND Voltage         | V <sub>ss</sub> -0.3 to V <sub>DD</sub> +0.3   |      |

| V <sub>CPP</sub>                                                 | CPP to PGND Voltage                  | $V_{PGND}$ -0.3 to $V_{DD}$ +0.3               |      |

| V <sub>CPN</sub> CPN to PGND Voltage                             |                                      | V <sub>SS</sub> -0.3 to V <sub>PGND</sub> +0.3 |      |

| TJ                                                               | Maximum Junction Temperature         | 150                                            |      |

| T <sub>STG</sub>                                                 | Storage Temperature Range            | -65 to +150                                    | °C   |

| T <sub>SDR</sub> Maximum Soldering Temperature Range, 10 Seconds |                                      | 260                                            |      |

| P <sub>D</sub> Power Dissipation                                 |                                      | Internally Limited                             | W    |

|                                                                  |                                      |                                                |      |

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions**

| Cymbol                                                        | Parameter                                                                                                                            | Rar  | Unit            |           |    |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|-----------|----|

| Symbol                                                        | raiametei                                                                                                                            | Min. | Max.            | Onic      |    |

| $V_{DD}$                                                      | Supply Voltage                                                                                                                       |      | 3               | 3.6       |    |

| V <sub>IH</sub>                                               | High Level Threshold Voltage                                                                                                         | DN   | 1.0             | -         | V  |

| V <sub>IL</sub>                                               | Low Level Threshold Voltage SDN                                                                                                      |      | -               | 0.35      |    |

| T <sub>A</sub>                                                | Operating Ambient Temperature Range                                                                                                  |      | -40             | 85        | °C |

| TJ                                                            | Operating Junction Temperature Range                                                                                                 | -40  | 125             | °C        |    |

| RL                                                            | Load Resistance                                                                                                                      |      | 600             | 100k      | Ω  |

| V <sub>IH</sub> V <sub>IL</sub> T <sub>A</sub> T <sub>J</sub> | High Level Threshold Voltage  Low Level Threshold Voltage  Operating Ambient Temperature Range  Operating Junction Temperature Range |      | -<br>-40<br>-40 | 85<br>125 |    |

#### **Thermal Characteristics**

| Symbol        | Parameter                                         | Typical Value | Unit |

|---------------|---------------------------------------------------|---------------|------|

|               | Thermal Resistance - Junction to Ambient (Note 2) |               |      |

| $\theta_{JA}$ | TSSOP-14                                          | 120           | °C/W |

| 2             | SOP-14                                            | 120           |      |

Note 2: Please refer to "Thermal Pad Consideration". 2 layered 5 in 2 printed circuit boards with 2oz trace and copper through several thermal vias. The thermal pad is soldered on the PCB.

TD9721

### **Electrical Characteristics**

$V_{\text{DD}}{=}3.3V,\ V_{\text{GND}}{=}V_{\text{PGND}}{=}0V,\ V_{\text{SDN}}{=}V_{\text{DD}},\ C_{\text{CPF}}{=}C_{\text{CPO}}{=}1\mu\text{F},\ C_{\text{i}}{=}1\mu\text{F},\ R_{\text{L}}{=}2.5k\Omega,\ T_{\text{A}}{=}25_{\text{o}}\text{C},\ R_{\text{i}}{=}10k\Omega,\ R_{\text{f}}{=}20k\Omega\ (\text{unless otherwise noted})$

| I <sub>DD</sub>       |                                                        | 1                                                                                                                                                                                                                               | Min. | Typ.                  | Max.              | Unit              |  |

|-----------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|-------------------|-------------------|--|

| I <sub>DD</sub>       |                                                        |                                                                                                                                                                                                                                 |      |                       |                   |                   |  |

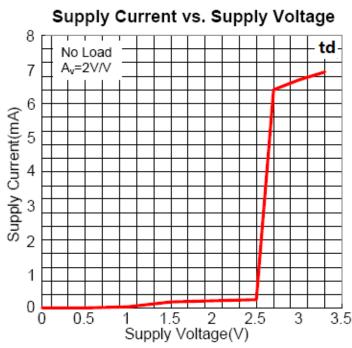

|                       | V <sub>DD</sub> Supply Current                         | V 0V                                                                                                                                                                                                                            | -    | 10                    | 15                | mA                |  |

| I <sub>SD</sub>       | V <sub>DD</sub> Shutdown Current                       | V <sub>SDN</sub> =0V                                                                                                                                                                                                            | -    | 1                     | 5                 | μΑ                |  |

| I <sub>I</sub>        | Input Current                                          | SDN                                                                                                                                                                                                                             | -    | 0.1                   | -                 | μΑ                |  |

| CHARGE PU             | 1                                                      | T I                                                                                                                                                                                                                             |      |                       | 1                 |                   |  |

| fosc                  | Switching Frequency                                    |                                                                                                                                                                                                                                 | 400  | 500                   | 600               | kHz               |  |

| R <sub>eq</sub>       | Equivalent Resistance                                  |                                                                                                                                                                                                                                 | -    | 21                    | 25                | Ω                 |  |

| DRIVERS               |                                                        |                                                                                                                                                                                                                                 |      |                       |                   |                   |  |

| $A_{vo}$              | Open Loop Voltage Gain                                 |                                                                                                                                                                                                                                 | 80   | 100                   | -                 | dB                |  |

| GW                    | Unity Gain Bandwidth                                   |                                                                                                                                                                                                                                 | 8    | 10                    | -                 | MHz               |  |

| $V_{\text{SR}}$       | Slew Rate                                              |                                                                                                                                                                                                                                 | -    | 4.5                   | -                 | V/μs              |  |

| $V_{\text{os}}$       | Output Offset Voltage                                  | $V_{DD}$ =3.0V to 3.6V, $R_{L}$ = 2.5k $\Omega$                                                                                                                                                                                 | -5   | -                     | 5                 | mV                |  |

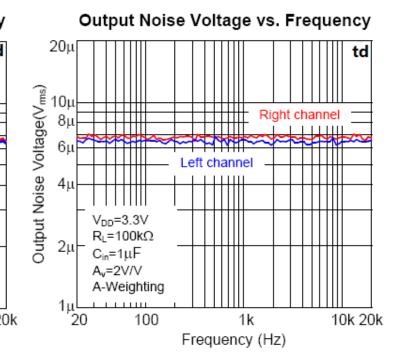

| $V_N$                 | Output Noise                                           | $R_i=10k\Omega$ , $R_f=10k\Omega$                                                                                                                                                                                               | -    | 8                     | 15                | μV <sub>rms</sub> |  |

| T <sub>start-up</sub> | Start-up Time                                          |                                                                                                                                                                                                                                 | -    | 500                   | -                 | μS                |  |

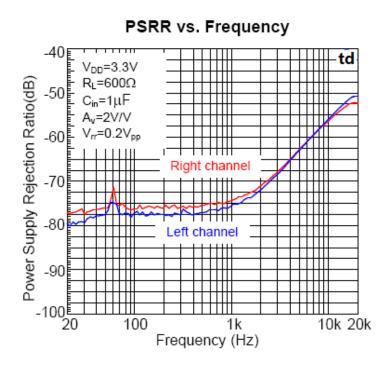

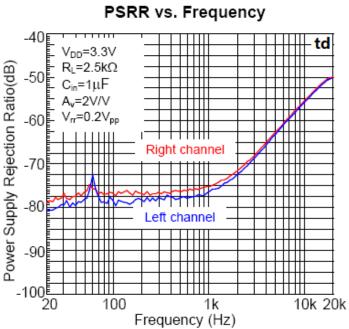

| PSRR                  | Power Supply Rejection Ratio                           | $V_{DD}$ =3.0V to 3.6V, $V_{rr}$ =200m $V_{rms}$<br>$f_{in}$ = 217Hz<br>$f_{in}$ = 1kHz<br>$f_{in}$ = 20kHz                                                                                                                     | -    | -80<br>-80<br>-50     | -60<br>-60<br>-45 | dB                |  |

| C <sub>L</sub>        | Maximum Capacitive Load                                |                                                                                                                                                                                                                                 | -    | 220                   | -                 | pF                |  |

| V <sub>ESD</sub>      | ESD Protection                                         | OUTR, OUTL                                                                                                                                                                                                                      | -    | 8                     | -                 | kV                |  |

| Vo                    | Output Voltage (Stereo, In<br>Phase)                   | THD+N=1%, $f_{in}$ =1kHz<br>R <sub>L</sub> =2.5kΩ<br>R <sub>L</sub> =100kΩ                                                                                                                                                      | 2.0  | 2.1<br>2.3            | -                 | ٧                 |  |

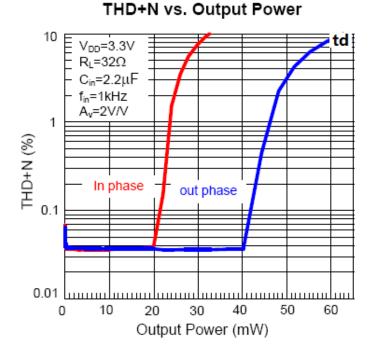

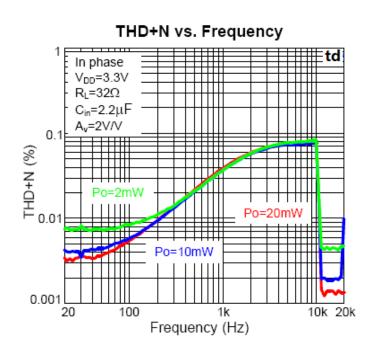

| Po                    | Output Power (Stereo, In<br>Phase)                     | THD+N=1%, $f_{in}$ =1kHz $R_L$ =32 $\Omega$                                                                                                                                                                                     | -    | 20                    | -                 | mW                |  |

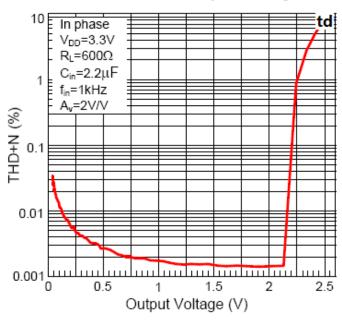

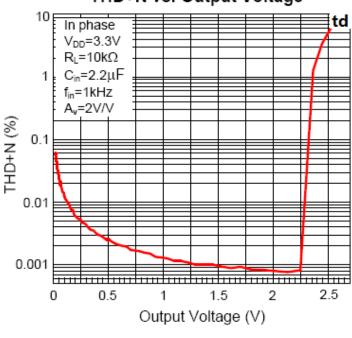

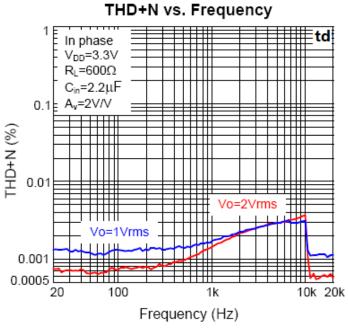

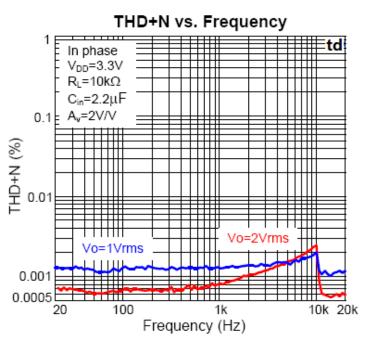

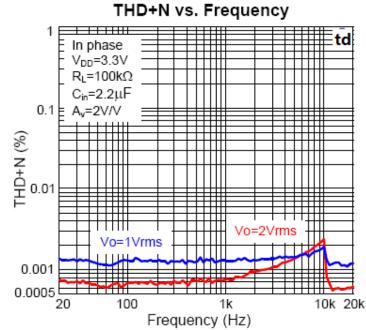

| THD+N                 | Total Harmonic Distortion Plus                         | $\begin{array}{l} V_{\text{O}}{=}2V_{\text{rms}},R_{\text{L}}{=}2.5k\Omega\\ f_{\text{in}}{=}20\text{Hz}\\ f_{\text{in}}{=}1\text{kHz}\\ f_{\text{in}}{=}20\text{kHz} \end{array}$                                              | -    | 0.02<br>0.001<br>0.02 | 0.002<br>-        | %                 |  |

| mb*n                  | Noise                                                  | Po=20mW, RL=32Ω<br>f <sub>in</sub> =1kHz                                                                                                                                                                                        | -    | 0.04                  | -                 | ,,                |  |

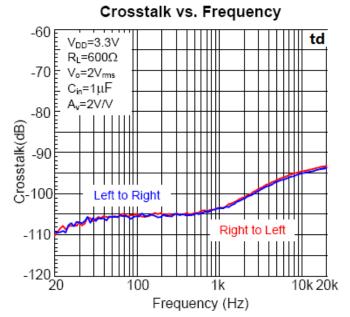

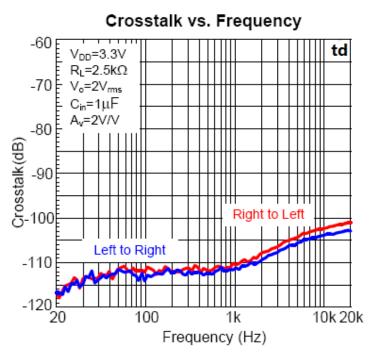

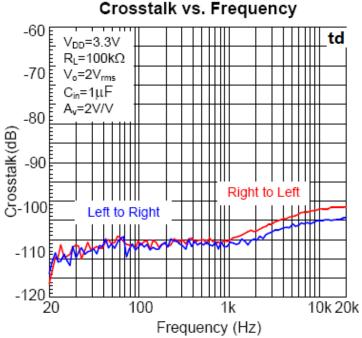

| Crosstalk             | Channel Separation                                     | $\begin{array}{l} V_{\text{O}}{=}2V_{\text{rms}},R_{\text{L}}{=}2.5k\Omega\\ f_{\text{in}}{=}20\text{Hz}\\ f_{\text{in}}{=}1\text{kHz}\\ f_{\text{in}}{=}20\text{kHz} \end{array}$                                              | -    | 100<br>100<br>90      | -                 | dB                |  |

| S/N                   | Signal to Noise Ratio                                  | $\begin{array}{l} V_{\text{O}}\text{=-}2\text{Vrms, } R_{\text{L}}\text{=-}2.5\text{k}\Omega, \ R_{\text{i}}\text{=-}10\text{k}\Omega, \\ R_{\text{i}}\text{=-}10\text{k}\Omega, \\ \text{With A-weighting Filter} \end{array}$ | -    | 108                   | 102               | dB                |  |

| T <sub>SD</sub>       | Thermal Shutdown Protection<br>Temperature             |                                                                                                                                                                                                                                 | -    | 150                   | -                 | °C                |  |

| UVP FUNCTION          | ON                                                     |                                                                                                                                                                                                                                 |      |                       |                   |                   |  |

| $V_{\text{UVP}}$      | External Under Voltage<br>Detection                    |                                                                                                                                                                                                                                 | -    | 1.25                  | -                 | V                 |  |

| I <sub>HYS</sub>      | External Under Voltage<br>Detection Hysteresis Current |                                                                                                                                                                                                                                 | -    | 5.0                   | -                 | μΑ                |  |

## TD9721

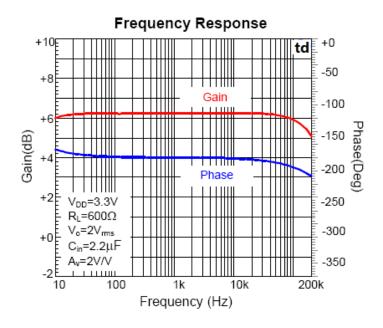

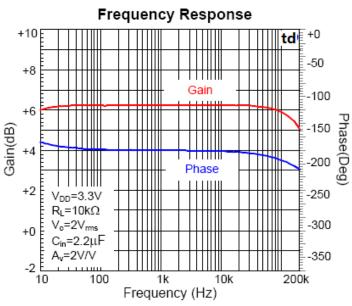

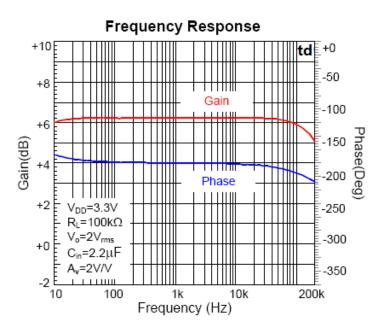

## **Typical Operating Characteristics**

### THD+N vs. Output Voltage

### THD+N vs. Output Voltage

### THD+N vs. Output Voltage

## TD9721

## **Typical Operating Characteristics(Cont.)**

## TD9721

## **Typical Operating Characteristics(Cont.)**

## TD9721

## **Typical Operating Characteristics(Cont.)**

### Output Noise Voltage vs. Frequency 20μ Output Noise Voltage(V<sub>ms</sub>) 10μ 8μ 6μ Left channel 4μ $V_{DD}=3.3V$ $R_L=600\Omega$ 2μ Cin=1µF A<sub>v</sub>=2V/V A-Weighting 100 20 10k 20k 1k Frequency (Hz)

## TD9721

## **Typical Operating Characteristics(Cont.)**

## **Type Application Circuit**

#### **Line Driver Amplifier**

#### 1. Inverting

#### 2. Non-Inverting

## **Type Application Circuit(Cont.)**

#### **Line Driver Amplifier (Cont.)**

#### 3. Differential

#### Second-Order Active Low-Pass Filter

#### 1. Differential

# **Type Application Circuit(Cont.)**

#### Second-Order Active Low-Pass Filter

#### 2. Inverting

### **Function Description**

#### **Line Driver Operation**

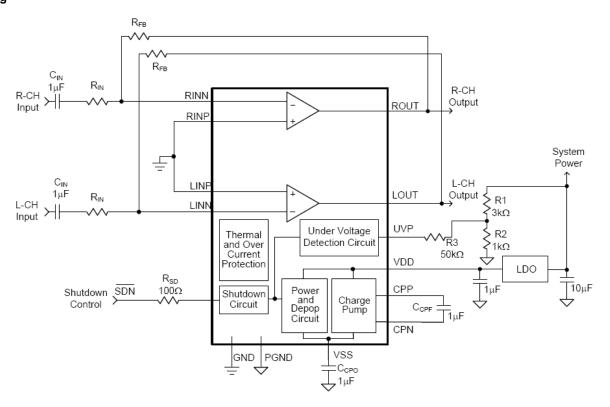

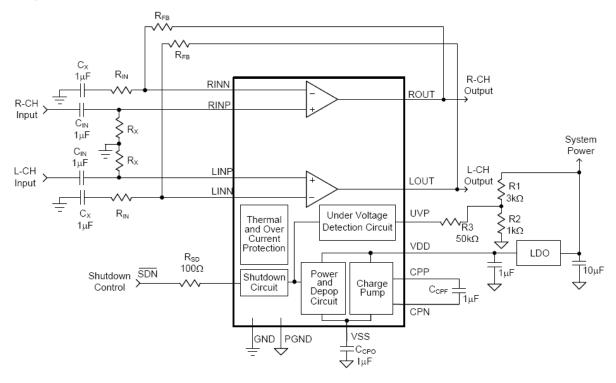

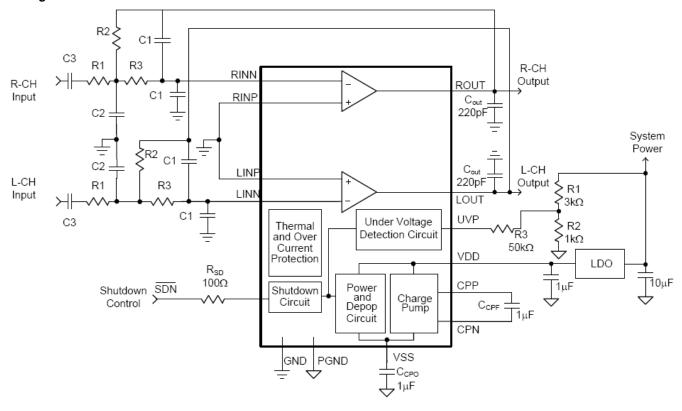

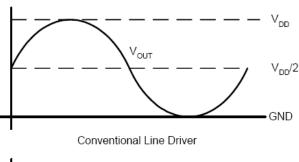

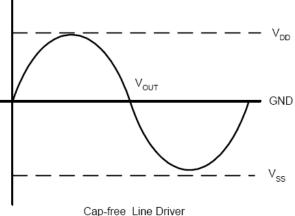

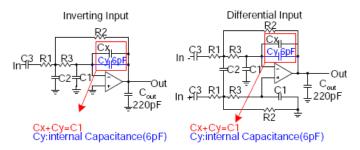

Figure 1. Cap-free Operation

The TD9721's line drivers use a charge pump to invert the positive power supply ( $V_{DD}$ ) to negative power supply ( $V_{SS}$ ), see figure1. The headphone drivers operate at this bipolar power supply ( $V_{DD}$  and  $V_{SS}$ ) and the outputs reference refers to the ground. This feature eliminates the output capacitor that is using in conventional single-ended headphone drive amplifier. Compare with the single power supply amplifier, the power supply range has almost doubled.

#### **Thermal Protection**

The thermal protection circuit limits the junction temperature of the TD9721. When the junction temperature exceeds T<sub>J</sub>=+150<sub>o</sub>C, a thermal sensor turns off the driver, allowing the devices to cool. The thermal sensor allows the driver to start-up after the junction temperature down about 125<sub>o</sub>C. The thermal protection is designed with a 25<sub>o</sub>C hysteresis to lower the average T<sub>J</sub> during continuous thermal overload conditions, increasing lifetime of the ICs.

#### **Shutdown Function**

In order to reduce power consumption while not in use, the TD9721 contains shutdown controllers to externally turn off the amplifier bias circuitry. This shutdown feature turns the amplifier off when logic low is placed on the SDN pins for the TD9721. The trigger point between a logic high is 1.0V and logic low level is 0.35V. It is recommended to switch between ground and the supply voltage V<sub>DD</sub> to provide maximum device performance. By switching the SDN pins to a low level, the amplifier enters a low-consumption current circumstance, charge pump is disabled, and I<sub>DD</sub> for the TD9721 is in shutdown mode. In normal operating, the TD9721's SDN pins should be pulled to a high level to keep the IC out of the shutdown mode. The SDN pins should be tied to a definite voltage to avoid unwanted circumstance changes.

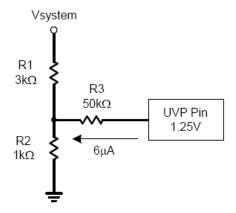

#### **Under-Voltage Protection**

External under voltage detection can be used to shutdown the TD9721 before an input device can generate a pop. The shutdown threshold at the UVP pin is 1.25V. The user selects a resistor divider to obtain the shutdown threshold and hysteresis for the specific application. The thresholds can be determined as below:

$VUVP = (1.25-6\mu AxR3) \times (R1+R2)/R2$

Hysteresis =  $5\mu A \times R3 \times (R1+R2)/R2$

With the condition: R3>>R1//R2

For example, to obtain Vuvp=3.8V and 1V hysteresis, R1=3k $\Omega$ , R2=1k $\Omega$  and R3=50k $\Omega$ .

Figure 2. Under-Voltage Protection

### TD9721

### **Application Information**

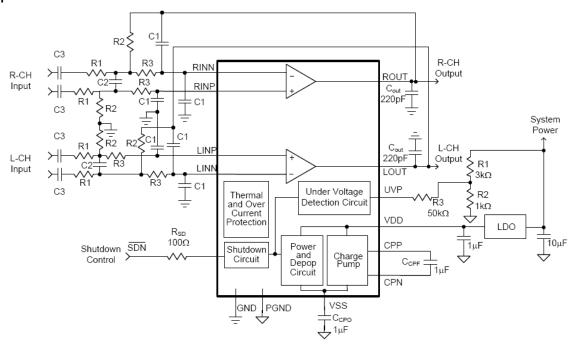

#### Using The TD9721 As A Second-Order Filter

Several audio DACs used today require an external lowpass filter to remove out-of-band noise. This is possible with the TD9721, as it can be used like a standard Operational Amplifier. Several filter topologies can be implemented, both single-ended and differential. In Figure3, a multi-feedback (MFB) with differential input and single-ended input is shown.

An ac-coupling capacitor to remove dc content from the source is shown; it serves to block any dc content from the source and lowers the dc-gain to 1, helping reducing the output dc-offset to minimum.

Figure 3. Second-Order Active Low-Pass Filter

| Gain<br>(V/V) | High<br>Pass<br>(Hz) | Low<br>Pass<br>(kHz) | C1<br>(pF) | C2<br>(pF) | C3<br>(μF) | R1<br>(kΩ) | R2<br>(kΩ) | R3<br>(kΩ) |

|---------------|----------------------|----------------------|------------|------------|------------|------------|------------|------------|

| -1            | 1.6                  | 40                   | 100        | 680        | 10         | 10         | 10         | 24         |

| -1.5          | 1.3                  | 40                   | 68         | 680        | 15         | 8.2        | 12         | 30         |

| -2            | 1.6                  | 60                   | 33         | 150        | 6.8        | 15         | 30         | 47         |

| -2            | 1.6                  | 30                   | 47         | 470        | 6.8        | 15         | 30         | 43         |

| -3.33         | 1.2                  | 30                   | 33         | 470        | 10         | 13         | 43         | 43         |

| -10           | 1.5                  | 30                   | 22         | 1000       | 22         | 4.7        | 47         | 27         |

For Inverting Input, The overall gain is:

$$A_V = -\frac{R2}{R1}$$

The high pass filter's cutoff frequency is:

$$f_{c(highpass)} = \frac{1}{2\pi R1C3}$$

The low pass filter's cutoff frequency is:

$$f_{c(lowpass)} = \frac{1}{2\pi\sqrt{R2R3C1C2}}$$

#### Input Capacitor, Ci

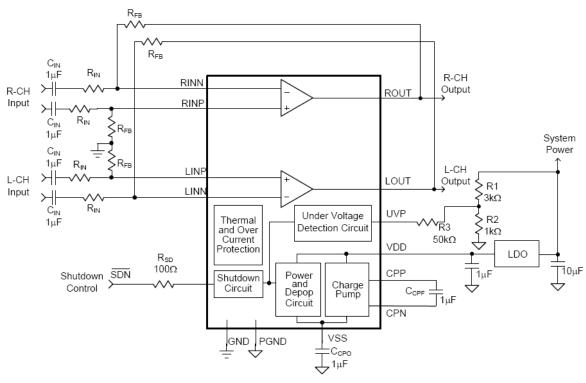

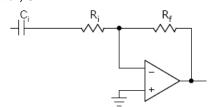

Figure 4. Typical Application Circuit

In the typical application, an input capacitor, C<sub>i</sub>, is required to allow the amplifier to bias the input signal to the proper DC level for optimum operation. In this case, C<sub>i</sub> and the minimum input impedance R<sub>i</sub> from a high-pass filter with the corner frequency are determined in the following equation:

$$f_{c(highpass)} = \frac{1}{2\pi R_i C_i}$$

The value of C<sub>i</sub> must be considered carefully because it directly affects the low frequency performance of the circuit.  $R_i$  is the external input resistance that typical value is  $10k\Omega$  and the specification calls for a flat bass response down to 20Hz. Equation is reconfigured as below:

$$C_i = \frac{1}{2\pi R_i f_{c(highpass)}}$$

When the input resistance variation is considered, the  $C_i$  is  $0.8\mu F$ , so a value in the range of  $1\mu F$  to  $2.2\mu F$  would be chosen. A further consideration for this capacitor is the leakage path from the input source through the input network ( $R_i + R_f$ ,  $C_i$ ) to the load.

This leakage current creates a DC offset voltage at the input to the amplifier that reduces useful headroom, especially in high gain applications. For this reason, a low leakage tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the negative side of the capacitor should face the amplifiers' input in most applications because the DC level of the amplifiers' input is held at GND. Please note that it is important to confirm the capacitor polarity in the application.

#### Input Resistor, Ri

The gain of the TD9721 is be set by the external input resistor ( $R_i$ ) and external feedback resistor ( $R_i$ ). Please see the figure 4.

### TD9721

## **Application Information(Cont.)**

#### Input Resistor, R: (Cont.)

$$Gain(A_{V}) = \frac{R_{f}}{R_{i}}$$

The external gain setting is recommended using from -1V/V to -10V/V, and the  $R_{\rm f}$  is in the range from  $1k\Omega$  to  $47k\Omega.$  It's recommended to use 1% tolerance resistor or better. Keep the input trace as short as possible to limit the noise injection. The gain is recommended to set -1V/V, and  $R_{\rm f}$  is  $10k\Omega,$  and  $R_{\rm f}$  is  $10k\Omega.$

#### Feedback Resistor, Rf

Refer the figure 4, the external gain is setting by  $R_i$  and  $R_f$ ; and the gain setting is recommended using from -1V/V to -10V/V. The  $R_f$  is in the range from  $4.7k\Omega$  to  $100k\Omega$ . It's recommended to use 1% tolerance resistor or better.

#### Power Supply Decoupling, Cs

The TD9721 is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure the output total harmonic distortion (THD+N) is as low as possible. Power supply decoupling also prevents the oscillations being caused by long lead length between the amplifier and the speaker.

The optimum decoupling is achieved by using two different types of capacitors that target on different types of noise on the power supply leads. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 0.1  $\mu F$ , is placed as close as possible to the device VDD and PVDD lead for the best performance. For filtering lower frequency noise signals, a large aluminum electrolytic capacitor of  $10\mu F$  or greater placed near the audio power amplifier is recommended.

#### Charge Pump Flying Capacitor, CCPF

The flying capacitor affects the load transient of the charge pump. If the capacitor's value is too small, then that will degrade the charge pump's current driver capability and the performance of line drive amplifier.

Increasing the flying capacitor's value will improve the load transient of charge pump. It is recommended using the low ESR ceramic capacitors (X7R type is recommended) above  $1\mu F$ .

#### Charge Pump Output Capacitor, Copo

The output capacitor's value affects the power ripple directly at  $CV_{SS}$  ( $V_{SS}$ ). Increasing the value of output capacitor reduces the power ripple. The ESR of output capacitor affects the load transient of  $CV_{SS}$  ( $V_{SS}$ ). Lower ESR and greater than  $1\mu F$  ceramic capacitor is a recommendation.

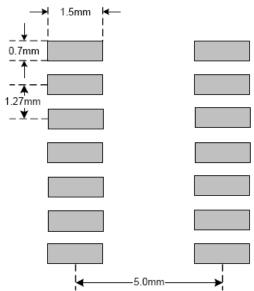

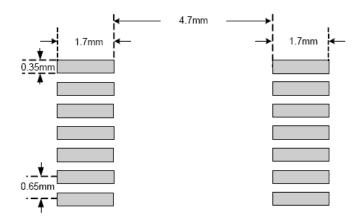

#### **Layout Recommendation**

SOP-14 Land Pattern Recommendation

TSSOP-14 Land Pattern Recommendation

TD9721

# **Package Information**

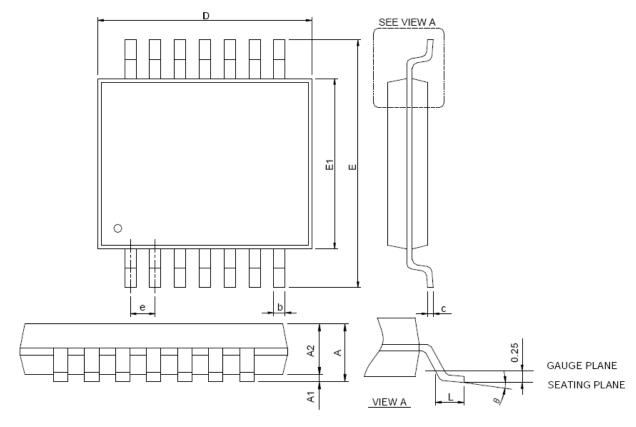

#### TSSOP-14

| S      | TSSOP-14 |      |        |       |  |  |

|--------|----------|------|--------|-------|--|--|

| SYMBOL | MILLIME  | TERS | INCHES |       |  |  |

| P      | MIN.     | MAX. | MIN.   | MAX.  |  |  |

| Α      |          | 1.20 |        | 0.047 |  |  |

| A1     | 0.05     | 0.15 | 0.002  | 0.006 |  |  |

| A2     | 0.80     | 1.05 | 0.031  | 0.041 |  |  |

| b      | 0.19     | 0.30 | 0.007  | 0.012 |  |  |

| С      | 0.09     | 0.20 | 0.004  | 0.008 |  |  |

| D      | 4.90     | 5.10 | 0.193  | 0.201 |  |  |

| Е      | 6.20     | 6.60 | 0.244  | 0.260 |  |  |

| E1     | 4.30     | 4.50 | 0.169  | 0.177 |  |  |

| е      | 0.65 BSC |      | 0.026  | 6 BSC |  |  |

| L      | 0.45     | 0.75 | 0.018  | 0.030 |  |  |

| 0      | 0°       | 8°   | 0°     | 8°    |  |  |

TD9721

# Package Information(Cont.)

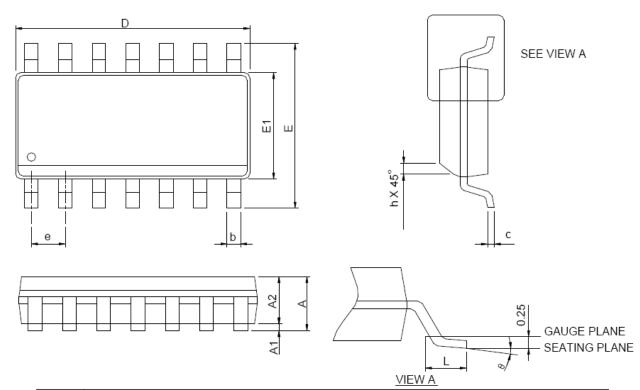

#### SOP-14

| S      | SOP-14   |       |        |       |  |

|--------|----------|-------|--------|-------|--|

| SYMBOL | MILLIM   | ETERS | INCHES |       |  |

| l C    | MIN.     | MAX.  | MIN.   | MAX.  |  |

| Α      |          | 1.75  |        | 0.069 |  |

| A1     | 0.10     | 0.25  | 0.004  | 0.010 |  |

| A2     | 1.25     |       | 0.049  |       |  |

| b      | 0.31     | 0.51  | 0.012  | 0.020 |  |

| С      | 0.17     | 0.25  | 0.007  | 0.010 |  |

| D      | 8.55     | 8.75  | 0.337  | 0.344 |  |

| E      | 5.80     | 6.20  | 0.228  | 0.244 |  |

| E1     | 3.80     | 4.00  | 0.150  | 0.157 |  |

| е      | 1.27 BSC |       | 0.050  | BSC   |  |

| h      | 0.25     | 0.50  | 0.010  | 0.020 |  |

| L      | 0.40     | 1.27  | 0.016  | 0.050 |  |

| θ      | 0°       | 8°    | 0°     | 8°    |  |

TD9721

**Design Notes**